Tecnologia di perforazione posteriore e PCB ad alta velocità

Progettazione PCB ad alta velocità e tecnologia di back drilling: la soluzione principale per l'integrità del segnale

Riassunto Nei settori delle comunicazioni 5G, dei server di intelligenza artificiale e dei data center ad alta velocità, i fori passanti per PCB (fori metallizzati) e la tecnologia di backdrilling (foratura a profondità controllabile) sono tecnologie chiave per garantire l'integrità del segnale e l'affidabilità del sistema. Questo articolo analizza sistematicamente la strategia di ottimizzazione della progettazione dei fori passanti nei PCB ad alta velocità, i principi fondamentali e il flusso di processo della tecnologia di backdrilling, e combina casi di riferimento di settore e dati di simulazione per fornire agli ingegneri una guida completa dalla teoria alla pratica, aiutando la progettazione di circuiti ad alta densità e alta frequenza a superare i colli di bottiglia prestazionali.

Sommario

1. PCB ad alta velocità tramite progettazione: dagli effetti parassiti alle strategie di ottimizzazione

1. Caratteristiche elettriche delle vie e sfide dell'integrità del segnale

In quanto canali di collegamento interstrato di PCB multistrato, i via (Via) presentano capacità parassita e induttanza parassita che influiscono significativamente sulla qualità del segnale in scenari ad alta frequenza:

• Formula della capacità parassita:

[ C = 1,41 \cdot \varepsilon_r \cdot T \cdot D_1 / (D_2 – D_1) ] Dove (\varepsilon_r) è la costante dielettrica, (T) è lo spessore della scheda, (D_1) è il diametro del pad e (D_2) è il diametro dell'area di isolamento.

• Formula dell'induttanza parassita:

[ L = 5,08h \left[ \ln(4h/d) + 1 \right] ] La lunghezza del via (h) e l'apertura (d) influenzano direttamente il valore dell'induttanza. L'induttanza di un via con apertura di 10 mil può raggiungere 1,2 nH a 1 GHz, con conseguente mutazione dell'impedenza.

Caso: in un progetto PCIe 4.0, la lunghezza dello stub di via superava i 200 mil, con conseguente chiusura dell'occhiello. Tramite il backdrilling, lo stub è stato mantenuto a meno di 50 mil e l'apertura dell'occhiello è stata aumentata di 40%.

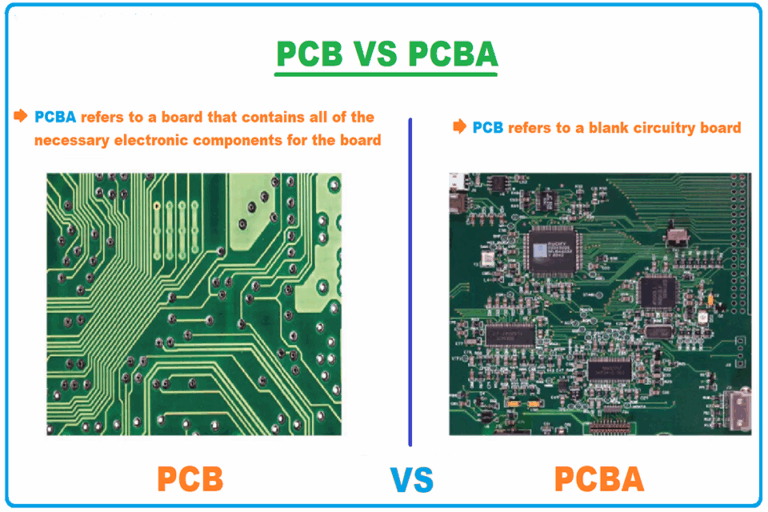

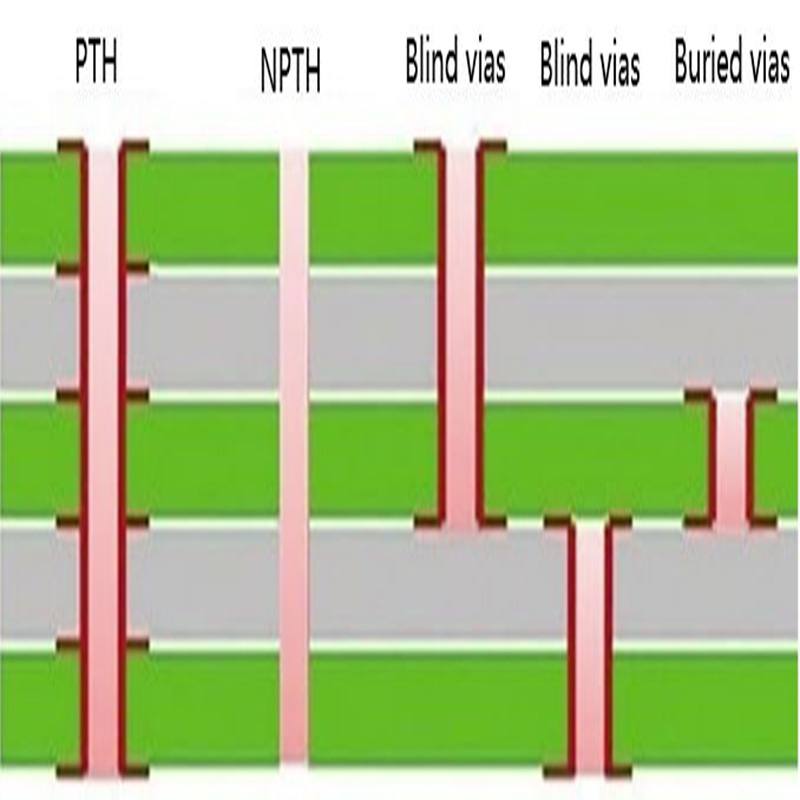

2. Confronto tra tipi di vie e scenari applicabili

| Tipo | Caratteristiche strutturali | Vantaggi | Limitazioni |

|---|---|---|---|

| Foro passante | Penetra l'intera tavola | Processo semplice e a basso costo | Tronchetto lungo, scarse prestazioni ad alta frequenza |

| foro cieco | Collega lo strato superficiale e lo strato interno | Riduce i monconi, adatto per alte densità | Richiede foratura laser, costo elevato |

| Buco sepolto | Collegamento tra strati interni | Nessun moncone, bassa perdita di segnale | Elevata complessità di produzione |

3. Sei regole d'oro per la progettazione di connessioni ad alta velocità

1.Ottimizzazione delle dimensioni:

• Progettazione generale: 0,25 mm/0,51 mm/0,91 mm (area di foratura/pad/isolamento);

• Scheda ad alta densità: 0,20 mm/0,46 mm/0,86 mm, con tecnologia non-through-hole (microvia).

2.Espansione dell'area di isolamento: seguire la regola D1=D2+0,41 per ridurre l'effetto capacità.

3.Strategia di routing a strati: ridurre il numero di modifiche di livello e utilizzare il layout differenziale simmetrico quando necessario.

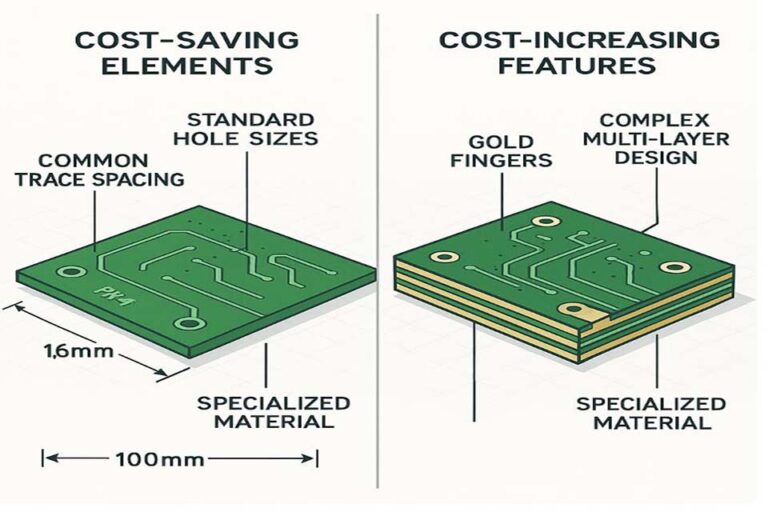

4.Priorità del pannello sottile: I PCB con spessore ≤1,6 mm possono ridurre i parametri parassiti di oltre 30%.

5.Ottimizzazione potenza/terra: praticare fori nelle vicinanze, lunghezza del cavo <0,5 mm, larghezza della linea ≥2 volte la linea del segnale.

6.Terra tramite array: posizionare i fori GND ogni 0,5 mm nell'area di cambio strato per accorciare il percorso di ritorno.

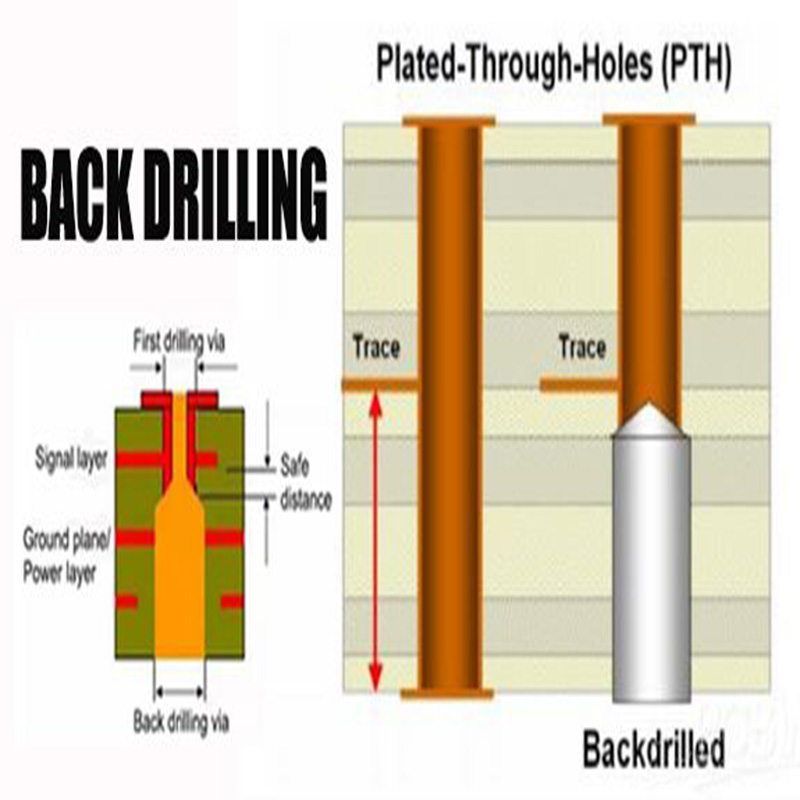

2. Processo di foratura posteriore: la soluzione definitiva per eliminare l'effetto moncone

1. Principio della tecnologia di perforazione posteriore e parametri del nucleo

La foratura posteriore (Back Drilling) rimuove i pilastri di rame inutilizzati (Stub) dei fori passanti mediante una foratura secondaria.

Gli indicatori tecnici chiave includono:

• Lunghezza residua dello stub (valore B): 50-150μm, per ogni aumento di 10μm del residuo, la perdita del segnale aumenta di 0,5dB a 10GHz.

• Tolleranza di apertura: ±0,05 mm, è richiesta una perforatrice CNC ad alta precisione.

• Controllo della profondità: utilizzando la tecnologia di rilevamento della microcorrente, la precisione del posizionamento raggiunge ±5μm.

Flusso di processo:

- Foratura primaria → 2. Sigillatura galvanica → 3. Produzione del modello dello strato esterno → 4. Posizionamento della foratura posteriore → 5. Foratura secondaria → 6. Lavaggio con acqua e rimozione dei trucioli.

2. Quattro principali vantaggi della tecnologia di backdrilling

• Integrità del segnale migliorata:

•ridurre la riflessione e la risonanza:e ridurre il tasso di errore di bit (BER) a meno di 10⁻¹².

• Efficacia dei costi: sostituire i requisiti dei fori ciechi e interrati 50% e ridurre la complessità della laminazione.

• Soppressione EMI: riduce il rumore irradiato di 6-8 dB e supera la certificazione FCC Classe B.

• Dflessibilità di progettazione: supporta scenari ad altissima velocità come i moduli ottici PAM4 112G.

3. Casi applicativi industriali

• Stazione base di comunicazione:La scheda Huawei 5G AAU utilizza la tecnologia back drilling per controllare lo stub entro 80 μm e la perdita di inserzione è <0,3 dB/mm a 28 GHz.

• Centro dati:La scheda carrier GPU NVIDIA A100 è ottimizzata tramite backdrilling e la velocità del segnale PCIe 5.0 è aumentata a 32 GT/s.

• Aerospaziale:Il PCB del satellite Lockheed Martin utilizza materiali a bassa perdita e perforazione posteriore per garantire la stabilità del segnale anche a temperature estreme.

4. Verifica della simulazione e tendenze tecnologiche future

1. Simulazione guidata tramite ottimizzazione

• Raccomandazione sugli utensili:

• Ansys HFSS: analisi del campo elettromagnetico a onda intera dei parametri della via S e della distribuzione del campo;

• Cadence Sigrity: verifica della continuità dell'impedenza tramite riflessione nel dominio del tempo (TDR).

• Caso: un progetto DDR5 ha rilevato il clock tramite deviazione del ritardo tramite simulazione e il jitter è stato ridotto da 15 ps a 8 ps dopo l'ottimizzazione.

2. Frontiere e sfide tecnologiche

• Materiali ad altissima frequenza:La costante dielettrica (Dk) delle schede della serie Rogers RO4500 è pari a 3,0, il che può ridurre la capacità di 30%.

• Foratura posteriore laser: La precisione è stata migliorata a ±10μm, supportando l'elaborazione di aperture da 0,1 mm.

• Integrazione di imballaggi 3D: TSV tramite tecnologia Silicon Via combinata con la perforazione posteriore del PCB per ottenere un packaging integrato eterogeneo.

Riepilogo

Nell'era digitale ad alta velocità, il design via e il processo di back drilling sono le leve fondamentali per le scoperte nelle prestazioni dei PCB. Controllando accuratamente i parametri parassiti, ottimizzando la lunghezza dello stub e combinando strumenti di simulazione avanzati (come Keysight ADS), gli ingegneri possono risolvere i problemi di integrità del segnale delle tecnologie all'avanguardia come 112G PAM4 e DDR6. In futuro, con l'innovazione dei materiali e gli aggiornamenti dei processi (come SevenpcbaGrazie alla soluzione di foratura posteriore a livello nano, i PCB continueranno a evolversi verso frequenze più elevate e una maggiore integrazione.