Hochgeschwindigkeits-PCB- und Rückbohrtechnologie

Hochgeschwindigkeits-PCB-Design und Back-Drilling-Technologie: die Kernlösung für Signalintegrität

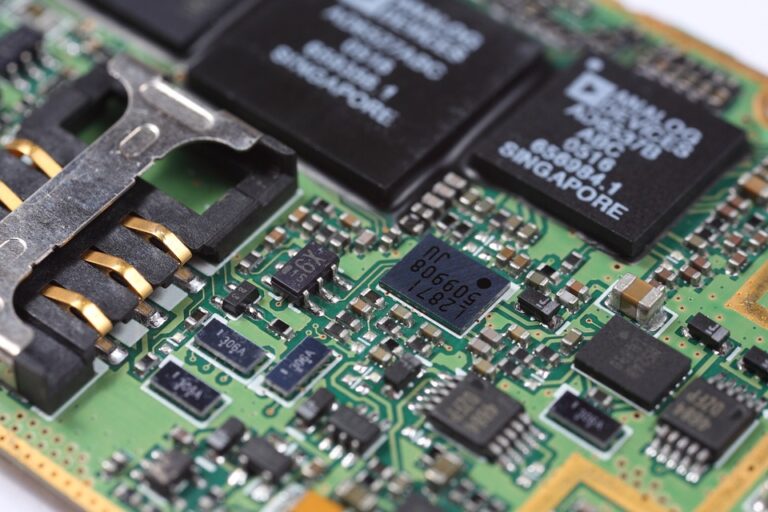

Zusammenfassung: In den Bereichen 5G-Kommunikation, KI-Server und Hochgeschwindigkeits-Rechenzentren sind PCB-Vias (metallisierte Löcher) und Backdrilling-Technologie (kontrollierte Tiefenbohrungen) Schlüsseltechnologien zur Gewährleistung der Signalintegrität und Systemzuverlässigkeit. Dieser Artikel analysiert systematisch die Optimierungsstrategie des Via-Designs in Hochgeschwindigkeits-PCBs, die Kernprinzipien und den Prozessablauf der Backdrilling-Technologie und kombiniert Branchen-Benchmarks und Simulationsdaten, um Ingenieuren einen umfassenden Leitfaden von der Theorie bis zur Praxis zu bieten und Leistungsengpässe bei der Entwicklung hochdichter und hochfrequenter Schaltungen zu überwinden.

Inhaltsverzeichnis

1. High-Speed-PCB-Via-Design: Von parasitären Effekten bis hin zu Optimierungsstrategien

1. Elektrische Eigenschaften von Vias und Herausforderungen hinsichtlich der Signalintegrität

Als Verbindungskanäle zwischen den Schichten mehrschichtiger Leiterplatten weisen Durchkontaktierungen (Via) parasitäre Kapazitäten und parasitäre Induktivitäten auf, die die Signalqualität in Hochfrequenzszenarien erheblich beeinträchtigen:

• Formel für die parasitäre Kapazität:

[ C = 1,41 \cdot \varepsilon_r \cdot T \cdot D_1 / (D_2 – D_1) ] Wobei (\varepsilon_r) die Dielektrizitätskonstante, (T) die Plattendicke, (D_1) der Pad-Durchmesser und (D_2) der Durchmesser des Isolationsbereichs ist.

• Formel für parasitäre Induktivität:

[ L = 5,08h \left[ \ln(4h/d) + 1 \right] ] Die Via-Länge (h) und die Apertur (d) wirken sich direkt auf den Induktivitätswert aus. Die Induktivität einer 10mil Apertur-Via kann bei 1GHz 1,2nH erreichen, was zu einer Impedanzänderung führt.

Fall: In einem PCIe 4.0-Design überschritt die Länge des Via-Stubs 200mil, was zu einem Augenschluss führte. Durch Backdrilling wurde der Stumpf auf unter 50mil reduziert und die Augenöffnung um 40% vergrößert.

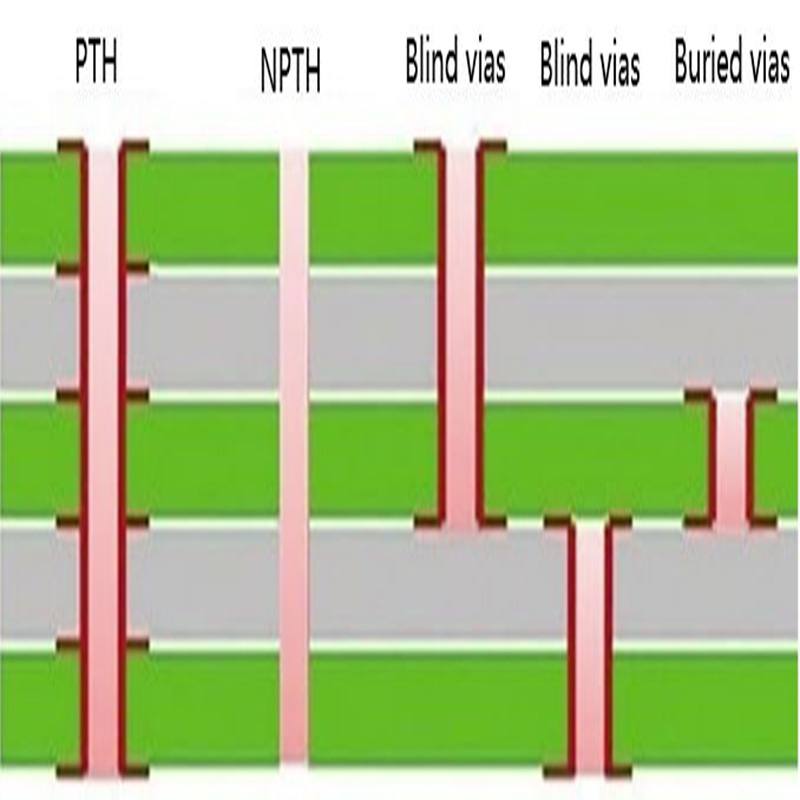

2. Vergleich von Via-Typen und anwendbaren Szenarien

| Typ | Strukturelle Merkmale | Vorteile | Einschränkungen |

|---|---|---|---|

| Durchgangsloch | Durchdringt das gesamte Brett | Geringe Kosten, einfacher Prozess | Langer Stummel, schlechte Hochfrequenzleistung |

| Sackloch | Verbindet die Oberflächenschicht mit der Innenschicht | Reduziert Stummel, geeignet für hohe Dichte | Erfordert Laserbohren, hohe Kosten |

| Vergrabenes Loch | Verbindung zwischen den Innenschichten | Kein Stub, geringer Signalverlust | Hoher Fertigungsaufwand |

3. Sechs goldene Regeln für das High-Speed-Via-Design

1.Größenoptimierung:

• Allgemeines Design: 0,25 mm/0,51 mm/0,91 mm (Bohr-/Pad-/Isolationsbereich);

• Hochdichte Platine: 0,20 mm/0,46 mm/0,86 mm, mit Non-Through-Hole-Technologie (Microvia).

2.Erweiterung des Isolationsbereichs: Befolgen Sie die Regel D1=D2+0,41, um den Kapazitätseffekt zu reduzieren.

3.Layer-Routing-Strategie: Reduzieren Sie die Anzahl der Lagenwechsel und verwenden Sie bei Bedarf ein differentielles symmetrisches Via-Layout.

4.Priorität für dünne Leiterplatten: Leiterplatten mit einer Dicke von ≤1,6 mm können parasitäre Parameter um mehr als 30% reduzieren.

5.Strom-/Erdungsoptimierung: Löcher in der Nähe bohren, Leitungslänge <0,5 mm, Leitungsbreite ≥2 mal die Signalleitung.

6.Masse über Array: Platzieren Sie im Lagenwechselbereich alle 0,5 mm GND-Vias, um den Rückweg zu verkürzen.

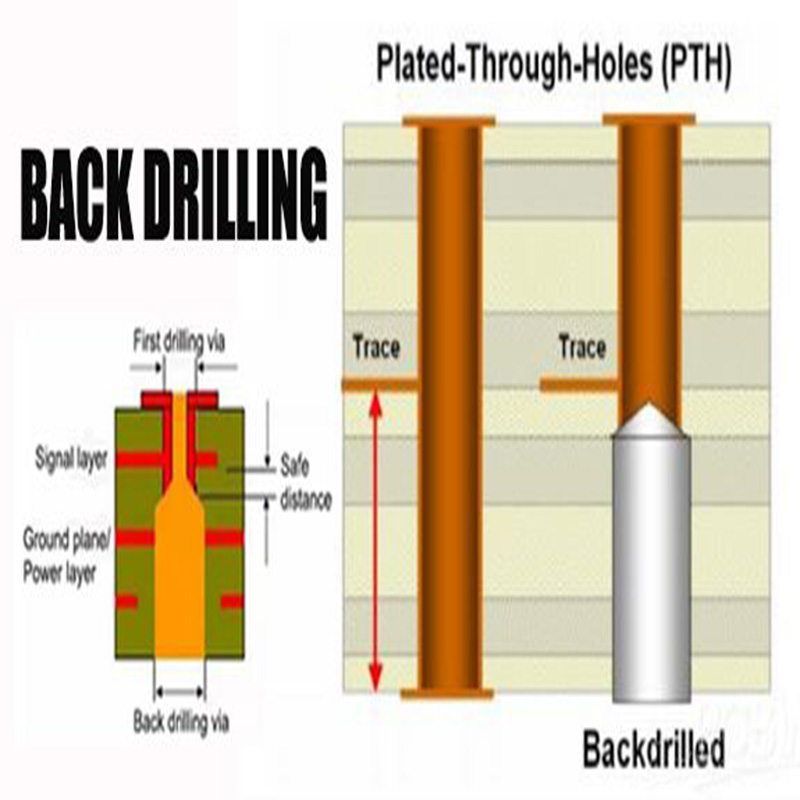

2. Rückbohrverfahren: Die ultimative Lösung zur Beseitigung des Stumpfeffekts

1. Prinzip und Kernparameter der Rückbohrtechnologie

Beim Rückbohren (Back Drilling) werden ungenutzte Kupferpfeiler (Stubs) von Durchgangslöchern durch Sekundärbohrungen entfernt.

Zu den wichtigsten technischen Indikatoren gehören:

• Stummelrestlänge (B-Wert): 50–150 μm, bei jeder Erhöhung des Restwerts um 10 μm erhöht sich der Signalverlust um 0,5 dB bei 10 GHz.

• Blendentoleranz: ±0,05 mm, hochpräzise CNC-Bohrmaschine erforderlich.

• Tiefenkontrolle: Durch den Einsatz der Mikrostromsensortechnologie erreicht die Positionierungsgenauigkeit ±5 μm.

Prozessablauf:

- Primärbohren → 2. Galvanisches Versiegeln → 3. Herstellung des Musters der äußeren Schicht → 4. Positionierung des Rückbohrens → 5. Sekundärbohren → 6. Waschen mit Wasser und Entfernen der Späne.

2. Vier wesentliche Vorteile der Backdrilling-Technologie

• Verbesserte Signalintegrität:

•Reduzieren Sie Reflexionen und Resonanzen:und die Bitfehlerrate (BER) auf unter 10⁻¹² reduzieren.

• Kosteneffizienz: Ersetzen Sie 50% durch die Anforderungen für Sacklöcher und vergrabene Löcher und reduzieren Sie die Laminierungskomplexität.

• EMI-Unterdrückung: Reduzieren Sie abgestrahltes Rauschen um 6–8 dB und bestehen Sie die FCC-Klasse-B-Zertifizierung.

• DDesignflexibilität: unterstützt Ultrahochgeschwindigkeitsszenarien wie optische 112G PAM4-Module.

3. Industrielle Anwendungsfälle

• Kommunikationsbasisstation: Die Huawei 5G AAU-Platine verwendet Back-Drilling-Technologie, um den Stub innerhalb von 80 μm zu steuern, und der Einfügungsverlust beträgt <0,3 dB/mm bei 28 GHz.

• Rechenzentrum: Die NVIDIA A100 GPU-Trägerplatine wird durch Backdrilling optimiert und die PCIe 5.0-Signalrate auf 32 GT/s erhöht.

• Luft- und Raumfahrt: Die Satelliten-Leiterplatte von Lockheed Martin verwendet Back Drilling und verlustarme Materialien, um die Signalstabilität bei extremen Temperaturen zu gewährleisten.

4. Simulationsverifizierung und zukünftige Technologietrends

1. Simulationsgetrieben durch Optimierung

• Werkzeugempfehlung:

• Ansys HFSS: Vollwellen-elektromagnetische Feldanalyse der Via-S-Parameter und Feldverteilung;

• Cadence Sigrity: Überprüfung der Impedanzkontinuität durch Time Domain Reflection (TDR).

• Fall: Ein DDR5-Design ermittelte den Takt über die Verzögerungsabweichung durch Simulation und der Jitter wurde nach der Optimierung von 15 ps auf 8 ps reduziert.

2. Technologische Grenzen und Herausforderungen

• Ultrahochfrequenzmaterialien: Die Dielektrizitätskonstante (Dk) der Platinen der Rogers RO4500-Serie beträgt nur 3,0, was die Via-Kapazität um 30% reduzieren kann.

• Laser-Rückseitenbohren: Die Genauigkeit wird auf ±10 μm verbessert und unterstützt die Verarbeitung einer 0,1-mm-Blende.

• 3D-Verpackungsintegration: TSV durch Silizium-Via-Technologie kombiniert mit PCB-Rückseitenbohrungen, um heterogene integrierte Verpackungen zu erreichen.

Zusammenfassung

Im Hochgeschwindigkeits-Digitalzeitalter sind Design und Back-Drilling-Prozesse die zentralen Hebel für PCB-Leistungsdurchbrüche. Durch die genaue Steuerung parasitärer Parameter, die Optimierung der Stichleitungslänge und die Kombination fortschrittlicher Simulationstools (wie z. B. Keysight ADS) können Ingenieure die Signalintegritätsprobleme von Spitzentechnologien wie 112G PAM4 und DDR6 lösen. In Zukunft, mit Materialinnovationen und Prozess-Upgrades (wie z. SevenpcbaMit der Nano-Level-Back-Drilling-Lösung von werden sich PCBs weiterhin in Richtung höherer Frequenzen und höherer Integration entwickeln.